WDC provides the following Data Deliverables in our technology transfer.

| Hard Core | ||||||||||||||||

|

||||||||||||||||

| Viewlogic Files | ||||||||||||||||

|

||||||||||||||||

| Soft Core | ||||||||||||||||

|

||||||||||||||||

| Firm Core | ||||||||||||||||

|

||||||||||||||||

| Common Files | ||||||||||||||||

|

||||||||||||||||

N/A – Not Applicable

NP – Not Planned

UC – Under Construction

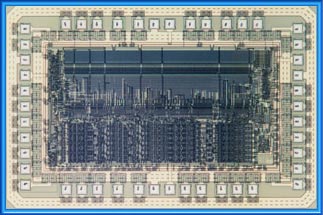

The W65C816 Hard Core is a manually optimized full custom hard core that has been used in millions of applications.

The W65C816 Hard Core has been manufactured in 3um, 2um, 1.5um, 1.2um, and 0.8um.

WDC’s microprocessor IP has been tailored for ease of reuse. The hard core IP is in the industry standard GDSII format.The buffer ring has been designed with off-chip drivers, including latch-up and ESD protection. When the core is embedded,the off-chip buffer ring is replaced with On-Chip-Bus (OCB) interface ring. The abstract cell is the connecting points with labels that provide core verification and system verification. WDC’s test programs require that all test pins be compared to the standard test vendors.

W65C816 Soft Core (RTL model)

The W65C816 Soft Core is a RTL (Register Transfer Level) description in Verilog HDL (Hardware Description Language) and is a synthesizable model. This single clock logic architecture is technology independent. WDC’s W65C816 Soft Core is designed to replace the industry standard W65C816 16-bit microprocessor and can be used as a drop-in replacement is ASIC’s. It has been synthesized into the XC4085 FPGA technology from Xilinx. The behavioral model is equivalent to the original W65C816 hard core. The standard chip model includes the softcore and the buffer ring in RTL code. If a minimum amount of gates are needed, the hard core of the W65C816C should be used.

FPGA Implementation Results

Implementation Results for the W65C816S in the LatticeXP Device

The following are typical performance and utilization results.

|

||||||||||||||