Introduction

The 6502 has had a proven value in education for over 4 decades. From Apple computers in classrooms to DIY breadboard kits, this pioneering Addressable Register-Instruction Set Architecture has been used to teach millions of learners worldwide. WDC has proudly supported educational institutions and continues to do so. In 2005, WDC supported the Introduction to VLSI Design with System on Chip Design Reuse: A Tutorial for Students. This tutorial was created in the absence of a VLSI course that Bill Mensch taught at ASU East. The tutorial focused on the W65C122S, a GDSII-based microcontroller featuring the W65C02, W65C22, RAM, and ROM. The design from this tutorial was taped out once through Tanner Research and MOSIS, however, the steps for tapeout are not covered in the tutorial. WDC continues to support professors and students of VLSI design, by offering chips, boards, and IP for student use at and within university Colleges of Engineering. 2023 will see these efforts continue as we work with partners and academia to provide Educational IP in both HDL and GDS form to enable new and improved VLSI, tapeout, and computing courses.

Read more about WDC’s Computing Intro to CHIPS STEM Education for Everyone Project Ideas below:

Loading…

Loading…

CHIPS Act SOC Design and Tapeout Classes built with WDC SOC IP

It is with the understanding that the world has begun what some refer to as the “Chip War” that WDC has decided to make available for educational purposes WDC critical IP, chips, and boards to support new engineering classes in VLSI Design with and without Tapeout options.

WDC, a 44-year-old company founded in 1978 has decided to enter the Chip War with support for introductory VLSI System-on-Chip (SOC) design and tapeout classes to be taught worldwide in Colleges of Engineering (COE). It is expected that after students learn the basic concepts of Systems-On-Chip (SOC) design with the legendary 6502 technology the students will graduate to RISC-V or ARM solutions for SOCs.

One of the many benefits of WDC’s use of Cadence tools, CMC Cloud Services, and partnering with Muse Semiconductor MPW services through TSMC, will be the lower cost of actually proving the SOC design in silicon on a test and evaluation board (TEB). WDC IP is flexible and can be used with any EDA software tool vendor, FPGA vendor, most Foundry processes, Cadence General PDK, and Open Source PDKs. Any support for Foundry PDK will be general and avoid the need for a multilateral NDA with the Foundry. Your institution will still need to work with your Foundry interface and IP vendors for access to Foundry PDKs, IO and Standard Cell Libraries, memory IP, etc.

Not only will these classes be taught with WDC’s Hardware Description Language (HDL) but also with WDC’s designs that are in production at TSMC using manually optimized chip designs. These same designs are available through Mouser in chip or board forms as well as other distributors (Where to Buy) for the convenience of student-designed boards.

The list of IP cores and SOC designs available through WDC’s Technology License Agreement (TLA) are:

WDC HDL Intellectual Property (IP)

WDC’s RTL-based HDL IP can be targeted to any FPGA vendor and most ASIC Foundry nodes.

Hardware Intellectual Property (IP)

- W65C02SOC40R SoC FPGA Microcontroller – Synthesizable HDL models

- Altera® FPGA Project Files and scripts. Support can be provided for retargeting to other FPGA families.

- W65C02RTL Microprocessor – Synthesizable HDL model

- W65C816RTL Microprocessor – Synthesizable HDL model

- W65C21RTL Peripheral Interface Adapter – Synthesizable HDL model

- W65C22RTL Versatile Interface Adapter – Synthesizable HDL model

- W65C51RTL Asynchronous Comm. Interface Adapter – Synthesizable HDL model

- W65CGPIO General Purpose IO – Synthesizable HDL model

- W65CWBI Wishbone Interface for I2C/SPI – Synthesizable HDL model

- W65CHBM Hardware Breakpoint – Synthesizable HDL model

Third-Party Hardware Intellectual Property (IP)

- Opencores.org I2C – Synthesizable HDL model

- Opencores.org SPI – Synthesizable HDL model

Software Intellectual Property (IP)

- W65C02SOC40 Monitor – Assembly source files and makefiles

- VIA/ACIA/I2C/SPI Libraries as available – Assembly/C source files and makefiles

WDC GDS Intellectual Property (IP)

Hardware Intellectual Property (IP)

WDC’s GDSII-based IP is based on 2000nm rule sets and can be targeted to most ASIC Foundry process nodes. WDC currently manufactures and sells GDSII-based chip products on the TSMC 600nm process.

- WDC_LibK Design Rules, Macros, and Std Cell Lib source files and executables

- W65C02 Microprocessor – GDSII, Netlists, Flowchart and Schematic

- W65C816 Microprocessor – GDSII, Netlists, Flowchart and Schematic

- W65C134 Microcontroller – GDSII, Netlists, and Schematic

- W65C265 Microcontroller – GDSII, Netlists, and Schematic

- W65C21 Peripheral Interface Adapter – GDSII, Netlists, and Schematic

- W65C22 Versatile Interface Adapter – GDSII, Netlists, and Schematic

- W65C51 Asynchronous Comm. Interface Adapter – GDSII, Netlists, and Schematic

- W65C256RAM 256 Byte RAM – GDSII, Netlists, and Schematic

- W65C4KROM 4096 Byte ROM – GDSII, Netlists, and Schematic

Software Intellectual Property (IP)

- W65C02SOC40 Monitor – Assembly source files and makefiles

- Assembly Tests – Assembly/C source files and makefiles

WDC IP License Process

Please let us know what you think of this revolutionary new approach to VLSI education. Contact Us if you are a professor at a College or University and are interested in integrating our IP into your existing or new course offering.

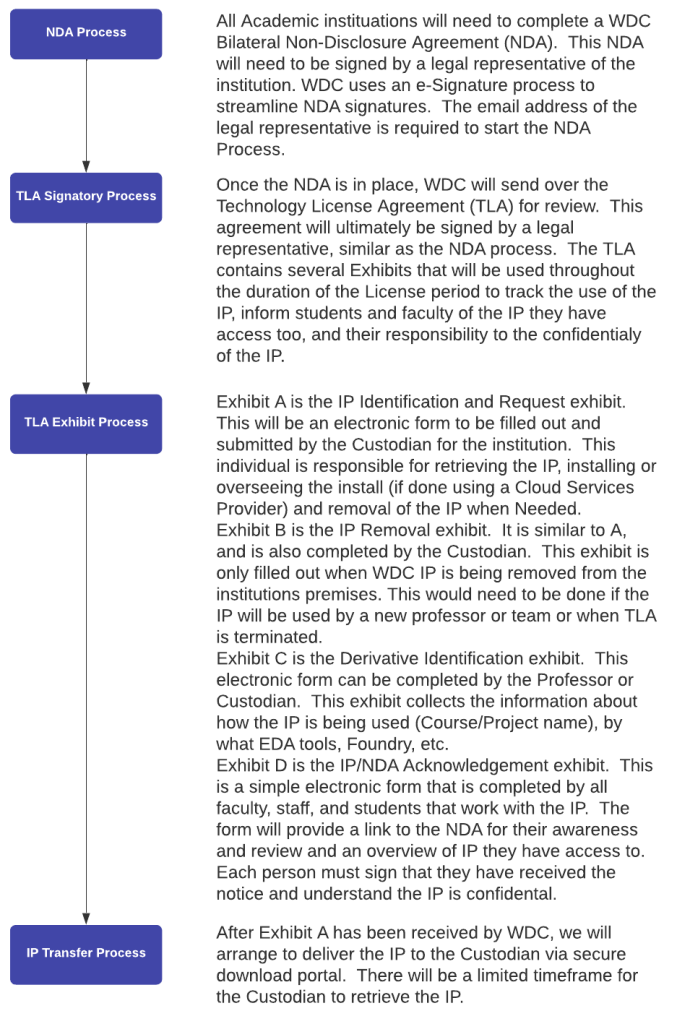

- To get started, WDC will provide a NDA for review by your institution’s legal review team. NDA will be electronically signed and tracked using Dropbox Sign. An email address of the signatory is needed for this process.

- Upon execution of the NDA, WDC will provide the Technology License Agreement (TLA) for review and discussion. TLA and Exhibits will be electronically signed and tracked using Dropbox Sign. An email address of the signatory is needed for this process.

- After a license is in place, IP and support requirements will be coordinated to best fit the needs of your course designs. All IPs will be transferred and tracked using Dropbox Transfer.

Orientation Sessions

Based on our current experiences with colleges and universities, we have found that having 30-minute – 1hr Zoom orientation sessions during the process improve communication and ease of getting started with WDC’s IP.

- Legal – This will cover any NDA and TLA questions and communication expectations.

- Professors – Covers IP handling, 6502 history and product evolution, design options, support needs, etc.

- Students – Covers IP handling, 6502 histories, and product evolution, design flow, professional and industry discussion, etc.

Feedback Requested

WDC is interested in feedback from Academia at both high school and college levels to validate our vision of the value and importance of WDC’s making our proprietary technology available for the next generations of engineers. This same technology has been licensed to companies throughout the world starting in 1981, the tenth anniversary of the first microprocessor.